最近看了看了一篇《vivado使用误区与进阶》的文章,觉得写得挺不错了,看完后自己对时序分析又有了更深一层的理解,故记录下来。可能排版有些乱,有些图都是直接从文章中截取,但是不影响阅读。

时序分析的基本步骤

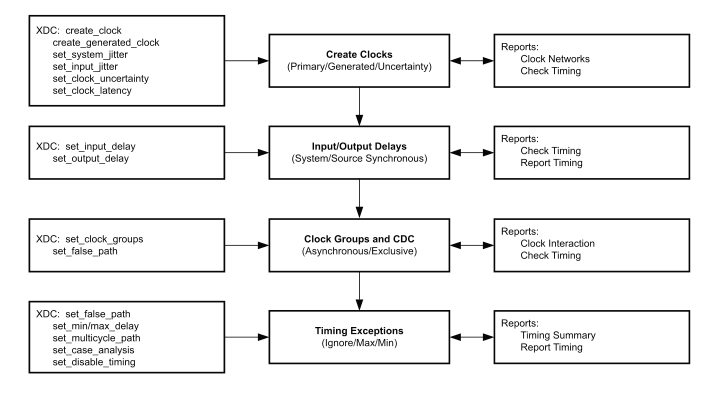

一个合理的时序约束,可以分为以下步骤:

时序约束整体的思路与之前我说的方法基本一致。整体的思路如下:

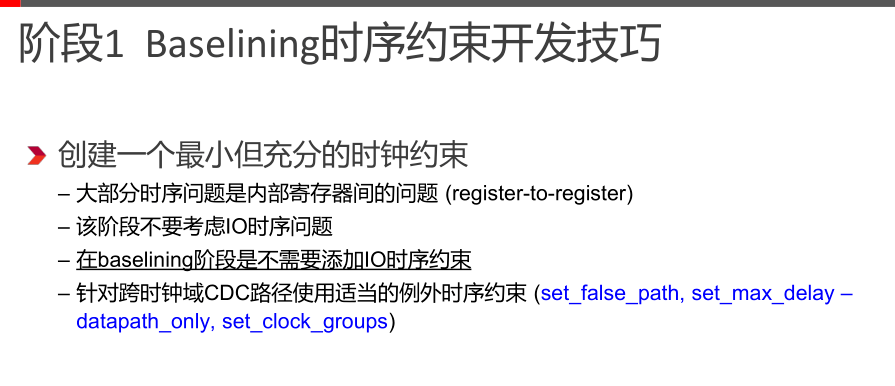

1. 先是约束时钟,让软件先解决内部时序问题;(在这一步骤中可以适当加入时序例外,以便时序通过)

2. 然后再加入IO的延迟约束;

3. 最后针对没有过的时序,添加时序例外。

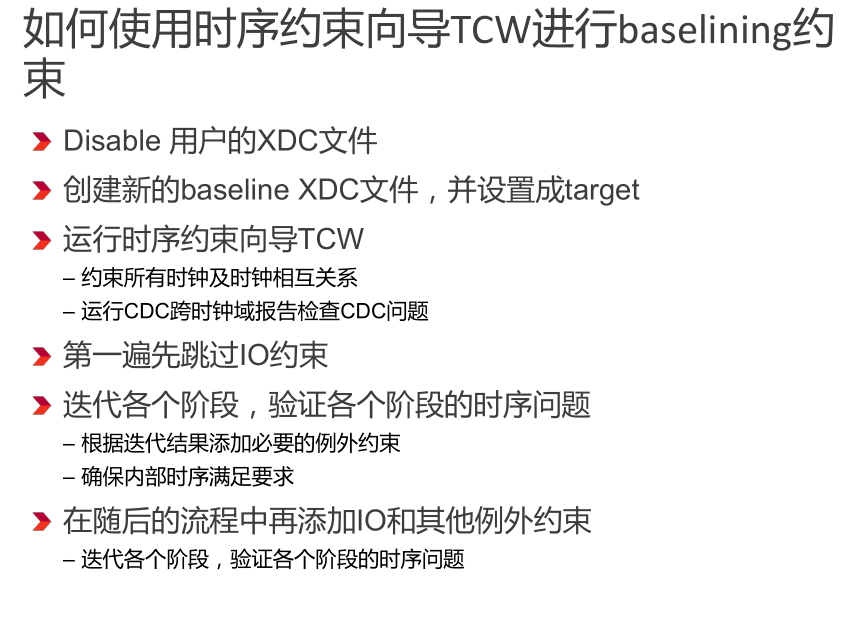

在《vivado使用误区与进阶》中,提到了一种叫 UltraFAST 的设计方法。针对下图中所说的根据迭代结果添加必要的例外约束(步骤1),为什么是添加必要的呢?是因为虽然是跨时钟域,但是有时候就算不约束,时序也能过。当碰到时序不过的时候,现阶段可以去针对该部分路径进行时序例外约束,以便后续继续分析。需要注意的是,就算没有报时序为例,现阶段也一定要去留意那些跨时钟的路径(通过clock_interaction),确认代码有没有做相应的跨时钟域处理。针对跨时钟域的代码处理后面会提到。

定义时钟约束

时钟主要可以分为主时钟以及衍生时钟。

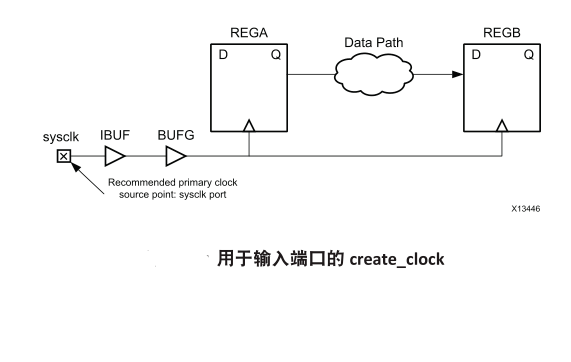

创建主时钟。典型的主时钟根包括有以下几种情况:输入端口、千兆位收发器输出引脚以及某些硬件原语输出管脚。

约束实例 :

create_clock -name SysClk -period 10 -waveform {0 5} [get_ports sysclk]

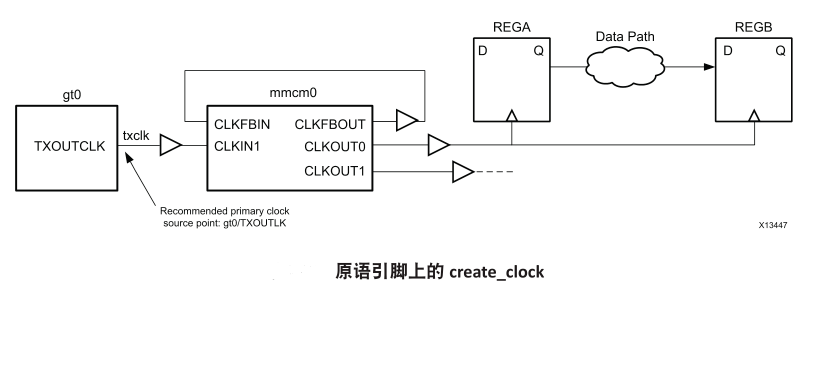

GT 收发器输入引脚,例如已恢复的时钟。

约束实例 :

create_clock -name txclk -period 6.667 [get_pin gt0/TXOUTCLK]

创建生成时钟

自动衍生时钟

• MMCM*/ PLL*

• BUFR

• PHASER*

如果 Vivado 设计套件时序引擎所选择的自动衍生时钟名称并不合适,您可以使用 create_generated_clock 命令强行定义自己的名称,此时无需指定波形转换。该约束应刚好位于约束文件中定义主时钟的约束之后。例如,由 MMCM 实例生成的时钟的默认名称是 net0,您可以添加如下约束强制将其设定为自己的名称(例如fftClk):

create_generated_clock -name fftClk [get_pins mmcm_i/CLKOUT0]

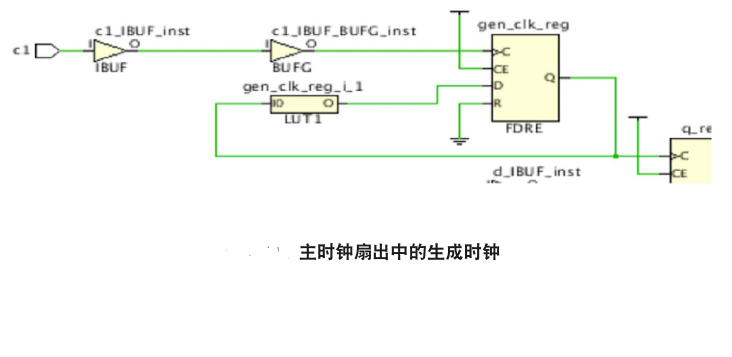

生成时钟源自另一个现有时钟(主时钟)。通常用来描述由逻辑模块在主时钟上执行的波形变换。由于生成时钟的定义取决于主时钟特性,因此必须首先定义主时钟。要明确定义生成时钟,必须使用 create_generated_clock 命令。

create_generated_clock -name GC1 -source [get_pins gen_clk_reg/C] -divide_by 2 [get_pins gen_clk_reg/Q]

跨时终域处理

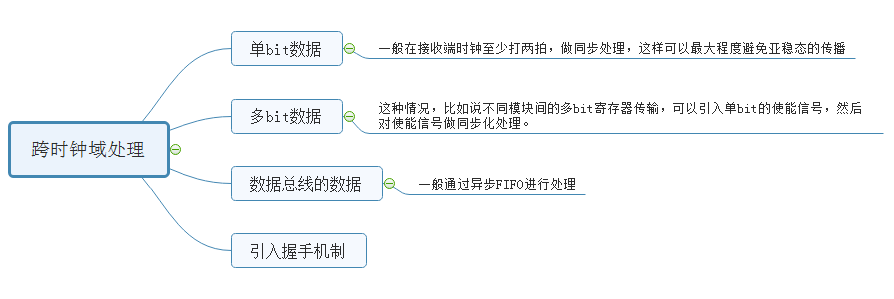

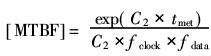

跨时钟域处理,主要是为了避免亚稳态的传播(注意亚稳态不能消除,但是可以采用一定的方式,降低其传播的风险)。触发器进入亚稳态的时间可以用参数MTBF(Mean Time Between Failures)来描述,MTBF即触发器采样失败的时间间隔,表示为:

例如针对单bit数据的跨时钟域处理,是为了让MTBF增大,使得进入一个可接受范围。

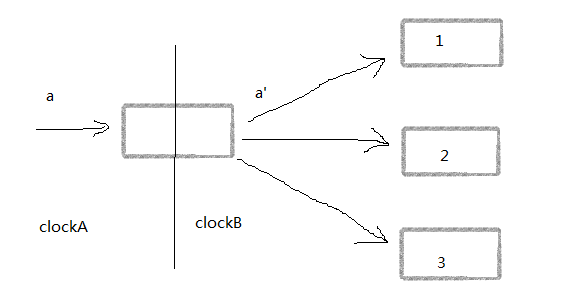

*跟大家探讨一个问题,为什么打两拍就可以降低亚稳态的传播呢?

我想到的一个场景如下:

信号a经过跨时钟处理后变成了a’;这样就可以确保在时序满足的前提下,同一个时钟域中的1、2、3模块接收到的a’的值是一致的,如果不做跨时钟域处理,由于布局布线的延迟不一样,不能确保到达1、2、3模块的值是一致的,从而导致逻辑混乱,引起系统的不稳定现象。

IO的延迟约束

输入延迟

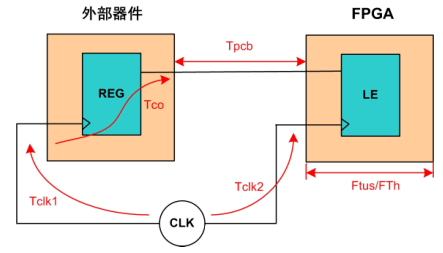

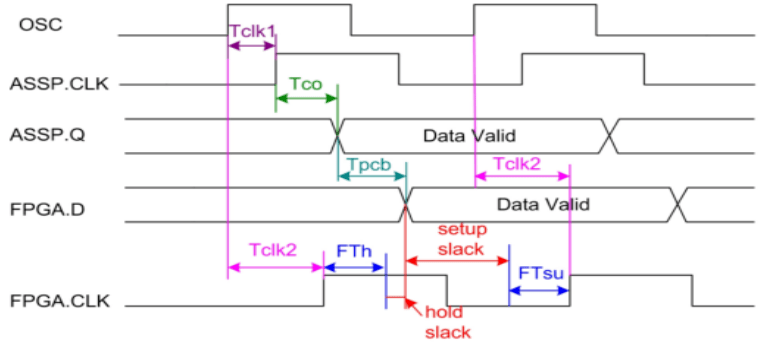

外部器件发送数据到FPGA系统模型如下图所示。对FPGA的IO口进行输入最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

输入延时即为从外部器件发出数据到FPGA输入端口的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、经过外部器件的数据发送Tco,再加上PCB板上的走线延时。如下图所示,为外部器件和FPGA接口时序。

最大输入延时(input delay max)为当从数据发送时钟沿(lanuch edge)经过最大外部器件时钟偏斜(Tclk1),最大的器件数据输出延时(Tco),再加上最大的PCB走线延时(Tpcb),减去最小的FPGA时钟偏移(FTsu)的情况下还能保证时序满足的延时。这样才能保证FPGA的建立时间,准确采集到本次数据值,即为setup slack必须为正,计算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +Tco(max) +Tpcb(max) +FTsu)≥0(1)

最小输入延时(input delay min)为当从数据发送时钟沿(lanuch edge)经过最小外部器件时钟偏斜(Tclk1),最小器件数据输出延时(Tco),再加上最小PCB走线延时(Tpcb),此时的时间总延时值一定要大于FPGA的最大时钟延时和建立时间之和,这样才能不破坏FPGA上一次数据的保持时间,即为hold slack必须为正,计算公式如下式所示:

Hold slack = (Tclk1(min) + Tco(min) + Tpcb(min))–(FTh + Tclk2(max))≥ 0(2)

我们很容易就可以从公式(1)和(2)推到出(3)

Tclk – Ftsu ≥Tclk1 - Tclk2 + Tco + Tpcb ≥ FTh(3)

在公式(3)中,我们发现Tclk 、Ftsu以及FTh,对于工具来说是已知的,而Tclk1 - Tclk2 + Tco + Tpcb正是我们需要告知综合工具的延迟量。

从我们推到出的公式,我们可以得到:

Input_delay_max = Tclk – Ftsu;

Input_delay_min = FTh ;

输出延迟

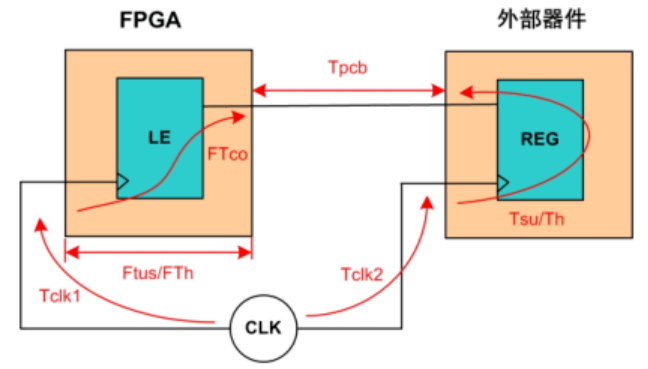

FPGA输出数据给外部器件模型如下图所示。对FPGA的IO口进行输出最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从第一级寄存器到输出端口之间的路径延迟,使其能够保证让外部器件能准确的采集到FPGA的输出数据。

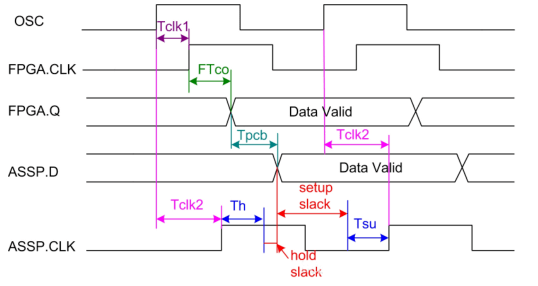

输出延时即为从FPGA输出数据后到达外部器件的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、PCB板上的走线延时以及外部器件的数据建立和保持时间。如所示,为FPGA和外部器件接口时序图。

最大输出延时(output delay max)为当从FPGA数据发出后经过最大的PCB延时、最小的FPGA和器件时钟偏斜,再加上外部器件的建立时间。约束最大输出延时,是为了约束IO口输出,从而使外部器件的数据建立时间,即为setup slack必须为正,计算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +FTco(max) +Tpcb(max) +Tsu)≥0(4)

最小输出延时(output delay min)为当从FPGA数据发出后经过最小的PCB延时、最大的FPGA和器件时钟偏斜,再减去外部器件的建立时间。约束最小输出延时,是为了约束IO口输出,从而使IO口输出有个最小延时值,防止输出过快,破坏了外部器件上一个时钟的数据保持时间,导致hlod slack为负值,不能正确的锁存到数据,最小输出延时的推导计算公式如下式所示:

Hold slack = (Tclk1(min) + FTco(min) + Tpcb(min))–(Th + Tclk2(max))≥ 0(5)

我们很容易就可以从公式(4)和(5),发现这两条公式与前面推导输入延迟如出一辙。只不过现在FPGA变成了输出器件,而Tsu、Th是下游器件的参数,综合工具并不知情,需要我们告诉他。除了FTco以外,其他参数都需要我们告诉工具。

由公式(4)我们可以推导出:

FTco(max) + Tpcb(max) –(Tclk2(min) – Tclk1(max)+Tsu ≤Tclk

那么output delay max = Tpcb(max) –(Tclk2(min) – Tclk1(max)+Tsu

同理我们由公式(5)可以推导出:

FTco(min) + Tpcb(min) – (Tclk2(max) – Tclk1(min))– Th ≥ 0

那么output delay min = Tpcb(min) – (Tclk2(max) – Tclk1(min))– Th

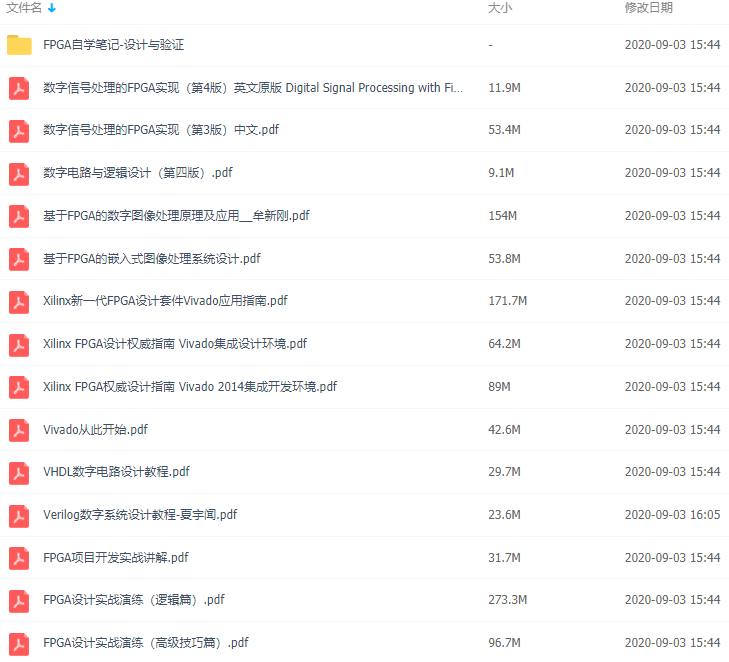

为了帮助学员能够更深入地掌握FPGA系统设计与实际应用。编者给大家准备了FPGA系列学习电子书籍,包括了 CPLD/Verilog编程语言基础与设计,数字IC、基本逻辑、组合逻辑等基础电路,Vivado平台开发与调试、集成开发环境使用及相关技巧,FPGA数字信号处理、数字图像处理及各种FPGA实战项目设计案例等等。

1.Verilog数字系统设计教程

本书从算法和计算的基本概念出发,讲述如何用硬线逻辑电路实现复杂数字逻辑系统的方法。全书共分三部分。部分内容共18章;二部分共12个上机练习实验范例;三部分是Verilog硬件描述语言参考手册,可供读者学习、查询之用。本书2版后,在语法篇中增加了IEEE Verilog1364-2001标准简介,以反映Verilog语法的新变化。

2.数字电路与逻辑设计

本书系统地阐述了逻辑电路的基础理论--逻辑函数及其数学工具;重点讨论了逻辑电路的设计方法和分析方法;详细介绍了通用性强的几类中、大规模集成器件,并结合实例介绍了它们在各领域中的应用;对可编程逻辑器件及其硬件描述语言也进行了系统介绍。

全书共10章,主要内容有:逻辑函数、集成逻辑门、组合逻辑电路、集成触发器、时序逻辑电路、硬件描述语言、半导体存储器、可编程逻辑器件、脉冲单元电路、模数及数模转换技术等。各章均附有内容提要、小结、思考题和习题。

3.Vivado从此开始

本书涵盖了Vivado的四大主题:设计流程、时序约束、设计分析和Tcl脚本的使用,结合实例深入浅出地阐述了Vivado的使用方法,精心总结了Vivado在实际工程应用中的一些技巧和注意事项,既包含图形界面操作方式,也包含相应的Tcl命令。本书语言流畅,图文并茂。全书共包含405张图片、17个表格、172个Tcl脚本和39个HDL代码,同时,本书配有41个电子教学课件,为读者提供了直观而生动的资料。本书可供电子工程领域内的本科高年级学生和研究生学习参考,也可供FPGA工程师和自学者参考使用。

4.Xilinx新一代FPGA设计套件Vivado应用指南

本书系统论述了新一代FPGA设计套件Vivado的性能、使用方法以及FPGA的开发方法。全书内容包括Vivado设计套件的特性,全面可编程FPGA器件的架构,使用Vivado套件创建复杂数字系统设计项目,仿真系统功能,RTL分析产生网表文件,性能要求的时序约束及综合,布局布线及静态时序分析和生成位流文件等全部设计过程,基于项目和非项目批作业两种用Tcl指令的设计模式,同步设计技术、HDL编码技术、时序收敛和HI.S优化DSP算法等关键技术,并以实例介绍了嵌入式系统的设计方法等。

5.Xilinx FPGA设计权威指南 Vivado集成设计环境

本书全面系统地介绍了Xilinx新一代集成开发环境Vivado的设计方法、设计流程和具体实现。全书共分8章,内容包括:Vivado设计导论、Vivado工程模式和非工程模式设计流程、Vivado调试流程、基于IP的嵌入式系统设计流程、Vivado HLS设计流程、System Generator设计流程、Vivado部分可重配置设计流程和Vivado高级设计技术。本书参考了Xilinx公司提供的Vivado最新设计资料,理论与应用并重,将Xilinx公司最新的设计方法贯穿在具体的设计实现中。

6.基于FPGA的嵌入式图像处理系统设计

本书详细介绍了FPGA这种新型可编程电子器件的特点,对FPGA的各种编程语言的发展历程进行了回顾,并针对嵌入式图像处理系统的特点和应用背景,详细介绍了如何利用FPGA的硬件并行性特点研制开发高性能嵌入式图像处理系统。作者还结合自己的经验,介绍了研制开发基于FPGA的嵌入式图像处理系统所需要的正确思路以及许多实用,并给出了许多图像处理算法在FPGA上的具体实现方法以及多个基于FPGA实现嵌入式图像处理系统的应用实例。

7.基于FPGA的数字图像处理原理及应用

本书首先介绍FPGA程序设计和图像与视频处理的关键基础理论,然后通过实例代码详细讲解了如何利用FPGA实现直方图操作中的直方图统计/均衡化/线性拉伸/规定化、线性滤波器操作中的均值滤波器、Sobel算子(滤波、求模、求角度)、非线性滤波器操作中的排序类算法/形态学滤波、图像分割算法中的局部自适应分割/Canny算子等。本书在仿真测试部分设计了一种完善的通用测试系统,并利用此测试系统在每一章的仿真测试环节对所设计算法进行严格的测试和验证。本书在很后一章介绍了在视频处理领域常见的输入/输出接口。本书偏向于工程应用,在书中有大量关于如何利用FPGA实现图像处理算法的实例及代码,并对这些算法的原理及其实现过程、算法测试等做了详细的介绍,全部的算法都进行了仿真测试验证。

8.数字信号处理的FPGA实现

FPGA仍旧是快速创新的领域,很高兴SpringerVerla9公司给我这个机会将FPGA领域的新发展囊括到本书的第3版中。本版新增了总计150多页全新的理念和当前的设计方法。第3版的创新主要包括以下几方面。

现在许多FPGA都包含嵌入式l8位×18位乘法器,因而推荐在以DSP为主的应用中使用这些器件,因为嵌入式乘法器可以节省很多LE。例如,在本版的所有示例,中都用到的CycloneIIEP2C35F672C6器件就具有35个18位×18位乘法器。

9.FPGA设计实战演练(逻辑篇+高级技巧篇)

FPGA设计实战演练共分为两册,分别是逻辑篇和高级技巧篇。

逻辑篇:主要面向广大的FPGA/CPLD初学者,从零基础开始讲述FPGA/CPLD以及相关的基础知识,并以一个支持各种入门、进阶的子母板形式的学习套件为实验平台,针对Altera公司的Cyclone Ⅲ器件量身打造的24个应用实例贯穿其中。实例讲解深入浅出,不仅有基本的Verilog语法讲解,也有设计思路和背景知识的详细描述; 开发工具(Quartus Ⅱ+ModelSim)的使用更是手把手、图文并茂地展示给读者。

高级技巧篇:现代FPGA的结构越来越复杂,多时钟域的设计现在已是常态。对于功能电路来说,复位结构都必不可少。在同步逻辑设计中如何很好地处理异步复位,甚至在多时钟域之间传递(异步)复位信号也是逻辑工程师经常面临的挑战。本书除专门介绍了上述电路的设计方法外,还介绍了状态机的设计。在介绍这些通用电路结构的基础上,还介绍了代码优化以及如何对设计进行综合与布局布线优化方面的相关内容。

10.FPGA项目开发实战讲解

本书立足于工程实践经验,首先介绍FPGA的原理、语法、设计技巧,然后详细介绍了7项常用技术的实现。每项技术从以下几方面介绍:相关技术介绍、FPGA方案框图设计、子模块设计、仿真和测试、项目开发过程中遇到的问题、定位和解决措施,其中插入了大量的状态机转换图和关键代码,方便读者学习。

FPGA工程师经典必读10+本全阶学习推荐书目,资料截图如下:

如何领取以上完整FPGA经典开发电子书?

扫一扫立即领取!

标签:进阶,FPGA,必学,器件,时序,延时,设计,时钟 来源: https://www.cnblogs.com/amxiang/p/15093527.html

本站声明: 1. iCode9 技术分享网(下文简称本站)提供的所有内容,仅供技术学习、探讨和分享; 2. 关于本站的所有留言、评论、转载及引用,纯属内容发起人的个人观点,与本站观点和立场无关; 3. 关于本站的所有言论和文字,纯属内容发起人的个人观点,与本站观点和立场无关; 4. 本站文章均是网友提供,不完全保证技术分享内容的完整性、准确性、时效性、风险性和版权归属;如您发现该文章侵犯了您的权益,可联系我们第一时间进行删除; 5. 本站为非盈利性的个人网站,所有内容不会用来进行牟利,也不会利用任何形式的广告来间接获益,纯粹是为了广大技术爱好者提供技术内容和技术思想的分享性交流网站。