这个问题应该分为两个:FPGA高速接口协议, FPGA PCIE 功能运用。

如果FPGA 来做PCIE 的话,X,A 厂的PCIE phy,link,trans layer 都是硬核 + logic实现,并且IP接口,驱动, 厂商均已经提供好,如果要运用PCIE 的话,直接使用对应的IP+Driver即可。

- FPGA高速接口协议:

Phy

需要用到,Tranciver(收发器 单lane可达30Gbps) 和 Serdes(普通高速IO 单lane可达 1.5Gbps)。所以只需要熟悉并掌握对应的文档和应用即可,最好结合实际硬件进行学习。

协议IP

最主要的是阅读 协议文档,并了解自己需要实现协议的哪一部分。可以去 opencore,github上去翻翻看别人的代码。

Eth 提供的Phy + Mac 层IP, 上层需要 自己实现。(阅读相关文档,或者使用IP 对应的driver, 嵌入式软件实现)。

Sata 厂商提供 Phy。 link, trans layer + driver 均需要自己实现。

Pcie 可以不用管协议直接使用xdma 等IP,或者使用比较基础的pcie IP(xdma 内部就是 pcie ip + dma ip)自己实现TLP (传输层协议)。大部分运用使用官方IP即可(xilinx windows 驱动问题较多)。

- FPGA PCIE 功能运用:

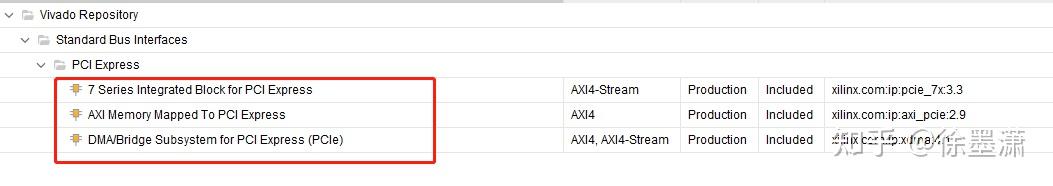

以xilinx为例

第一个IP 直接封装硬核 需要自己去封装TLP 包,可以生成Example 去查看TLP 相关协议如何工作。运用的使用还需要再stream外层对数据进行打包,比较复杂。

第二个IP 就是将IP 封装为AXI Mem接口,对外直接读写数据,无法看到协议控制等内容。并且驱动以及IP控制没有提供sgdma 的方式,应用层内存管理较为复杂。

第三个IP 算是用的最多的,在第二个基础上增加了SGDMA 的功能,Root端运用非常方便。Example 直接可以在 windows/linux/mac 上运行。

(这个IP的windows驱动问题较多,不过勉强可用)。

PCIe研究的人挺多的,网上资料也很多。

1、先在网上搜PCIe关键字,把各个论坛、博客上相关内容都熟悉一下,建立对PCIe体系结构的初步概念。

2、需要阅读pcie spec,可以配合MINDSHARE的PCI Express Technology,这一步可能需要反复重复才能弄懂。

3、看懂XILINX/INTEL等FPGA原厂PCIe IP的datasheet。

4、可以用官方PCIe Example,在开发板上跑起来。

还要看你学习的目的,如果你的目的是精通PCIe协议本身,那么最重要的是上述第2步,如果你的目的仅仅是把PCIe用起来,那就简单了,FPGA原厂提供各种功能完善的PCIe IP,比如XILINX的PCIe AXI Bridge等IP,这些IP已经把复杂的PCIe接口屏蔽,用户面对的是相对简单的AXI接口。

楼上也提到MINDSHARE,去MINDSHARE官网看看,不光是PCIe,很多高速接口协议,比如SATA、NVMe、USB等等,它们都有出详解。

标签:协议,FPGA,PCIe,IP,接口协议,PCIE 来源: https://www.cnblogs.com/amxiang/p/15710502.html

本站声明: 1. iCode9 技术分享网(下文简称本站)提供的所有内容,仅供技术学习、探讨和分享; 2. 关于本站的所有留言、评论、转载及引用,纯属内容发起人的个人观点,与本站观点和立场无关; 3. 关于本站的所有言论和文字,纯属内容发起人的个人观点,与本站观点和立场无关; 4. 本站文章均是网友提供,不完全保证技术分享内容的完整性、准确性、时效性、风险性和版权归属;如您发现该文章侵犯了您的权益,可联系我们第一时间进行删除; 5. 本站为非盈利性的个人网站,所有内容不会用来进行牟利,也不会利用任何形式的广告来间接获益,纯粹是为了广大技术爱好者提供技术内容和技术思想的分享性交流网站。