标签:语句 10 时间尺度 Verilog 赋值 延迟 tb ta

在Verilog的建模中,时间尺度和延迟是非常重要的概念,设置好时间尺度和延迟,可以充分模拟逻辑电路发生的各种情况和事件发生的时间点,来评估数字IC设计的各种要求,达到充分评估和仿真的作用。注意延迟语句是不可综合的,只是用来数据建模或仿真。

1. 时间尺度

语法格式: `timescale 10ns/1ns

用关键字 `timescale标识,后面跟时间刻度,如:10ns/1ns,其中10ns表示基本时间刻度,就是每10ns作为一个刻度。1ns是精度,一般在仿真软件中的最小刻度。不同的仿真工具的精度不同,在modelsim中一般时间刻度为1ps,与`timescale 10 ns/1 ps的1 ps的设置是等效的。

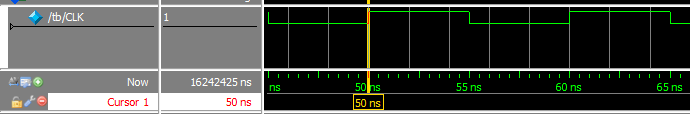

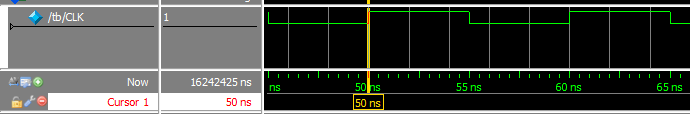

例:在testbench 中时钟的建模:

`timescale 1ns/1ps //时间刻度为1 ns

module top_sim

(

);

reg CLK;

initial

begin

CLK = 1'b0;

#5;

forever

#5 CLK = ~CLK; //duty cycle 50%, period 10 ns; Frequency 100Mhz;

end

endmodule

Modelsim 波形

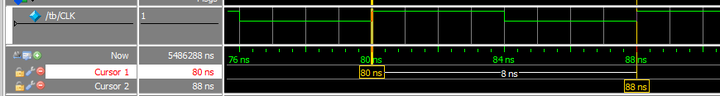

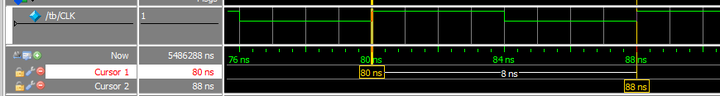

`timescale 1ns/1ps //时间刻度为1 ns

module top_sim

(

);

reg CLK;

initial

begin

CLK = 1'b0;

#4;

forever

#4 CLK = ~CLK; //duty cycle 50%, period 8 ns; frequency 125Mhz

end

endmodule

Modelsim 仿真波形

在设置时间尺度是也可直接指定时间单位或由关键字parameter定义的参数指定,修改缺省的 由`timeschale定义的时间尺度。

例:

parameter PERIOD = 10 ; reg CLK; initial begin CLK = 1'b0; #(PERIOD/2); forever #(PERIOD/2) CLK = ~CLK; end

2. 延迟:

赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端变量赋值之间的时间延时。

-

-

根据信号类型可分为连续赋值延时和寄存器赋值延时,

-

根据延迟特性分为内部延迟和外部延迟

-

连续赋值时延:一般可分为普通赋值时延、隐式时延、声明时延;只有 外部时延。

-

寄存器赋值延时:只有在使用时可分为内部时延 和 外部时延, 但没有声明延时。

例:

wire [3:0] a, b, c;

assign #10 c = a + b;

含义:a,b中有任意一个发生变化,将a+b的结果延时10个时间单位,赋值给变量c。

作用:在连续赋值期间,如果a+b的结果不断变化,c并不跟随a+b 结果的变化,直到a,b变量稳定后,在指定的10个时间单位延迟到达后才赋值。

`timescale 1 ns/1 ps

module tb

(

);

reg [3:0] ta,tb;

wire [3:0] tc ,td;

assign #10 tc = ta + tb;

assign #10 td = ta - tb;

initial

begin

ta = 4'b0000;

tb = 4'b0000;

#2

tb = 4'b0001;

#2

ta = 4'b0010;

#2

tb = 4'b0100;

#2

ta = 4'b0010;

tb = 4'b1000;

#2

ta = 4'b0110;

tb = 4'b0001;

#20

tb = 4'b0111;

tb = 4'b0110;

#20

tb = 4'b1111;

tb = 4'b0110;

end

endmodule

仿真波形如下:

从波形可以看出,虽然开始ta,tb 有多次变化,由于变化的时间间隔都不足10个单位,因此tc并没有得到ta+tb的结果,只有在ta==4’b0110, tb==4’b0001的时刻开始,ta,tb稳定持续10个时间单位后,tc才得到ta+tb的值。所以连续赋值语句能否更新,是从参与计算的变量最近的时刻是否满足延迟时间的需求而定。

wire A, B; wire #10 Z = A & B;

声明一个wire型变量时对其进行包含一定时延的连续赋值。

wire A, B; wire #5 Z ; assign Z =A + B;

声明时延,声明一个wire型变量时指定一个时延。因此对该变量所有的连续赋值都会被推迟到指定的时间。除非门级建模中,一般不推荐使用此类方法建模。

惯性延迟,如上面的例子

reg [3:0] ta, tb ;

wire [3:0] tc ,td;

assign #10 tc = ta + tb;

assign #10 td = ta – tb;

如果在这 10 个时间单位内,即在 td 获取新的值之前,ta 或 tb 任意一个值又发生了变化,那么计算 tc, td 的新值时会取 ta 或 tb 当前的新值。所以称之为惯性时延,即信号脉冲宽度小于时延时,对输出没有影响。

因此仿真时,时延一定要合理设置,防止某些信号不能进行有效的延迟。

按时延特性 可以分为:

延迟还分内部延迟(intra _delay)和外部延迟(inter_delay)两种。上面介绍的例子都是外部延迟。

内部延迟

intra_delay: 是指在赋值语句内部的延迟。看下面三条语句就可以明白intra_delay 和inter_delay的区别。

例1:

wire co, y; assign {co, y} = a + b + ci; assign # inter_delay {co, y} = a + b + ci;

语句assign {co, y} = a + b + ci; 是连续赋值语句,赋值语句的左边LHS(left hand side) {co,y}始终追随右边RHS的变化,右边任何一个变量发生变化,赋值语句立即评估结果,并赋给左边变量。

语句assign # inter_delay {co, y} = a + b + ci;是外部延时语句,当RHS变量有变化时,等待 # inter_delay时间后评估RHS的值,并赋给LHS变量。

例2:

reg co, y;

always@(*)

{co, y} = #intra_delay a + b + ci;

语句{co, y} = #intra_delay a + b + ci;是内部延时语句,用在赋值语句内部,当RHS变量有变化时,立即评估a+b+ci的结果,延迟#intra_delay时间后,将评估的结果赋给LHS变量。

注:内部延时语句只能用在顺序语句中。

例: module tb

(

);

reg [3:0] ta,tb;

wire [3:0] tc_inter, tc_intra ,td;

assign #10 tc_inter = ta + tb;

assign #10 td = ta - tb;

initial

begin

ta = 4'b0000;

tb = 4'b0000;

#2

tb = 4'b0001;

#2

ta = 4'b0010;

#2

tb = 4'b0100;

#2

ta = 4'b0010;

tb = 4'b1000;

#2

ta = 4'b0110;

tb = 4'b0001;

#5

tb = 4'b0111;

tb = 4'b0110;

#20

tb = 4'b1111;

tb = 4'b0110;

end

always@(*)

tc_intra = #10 ta + tb;

endmodule

仿真波形如下:

从仿真波形可以清楚看出,内部延迟与外部延迟的区别。

在建模时应注意各种delay的选择与使用。

标签:语句,10,时间尺度,Verilog,赋值,延迟,tb,ta

来源: https://www.cnblogs.com/c6c6c6/p/15147667.html

本站声明:

1. iCode9 技术分享网(下文简称本站)提供的所有内容,仅供技术学习、探讨和分享;

2. 关于本站的所有留言、评论、转载及引用,纯属内容发起人的个人观点,与本站观点和立场无关;

3. 关于本站的所有言论和文字,纯属内容发起人的个人观点,与本站观点和立场无关;

4. 本站文章均是网友提供,不完全保证技术分享内容的完整性、准确性、时效性、风险性和版权归属;如您发现该文章侵犯了您的权益,可联系我们第一时间进行删除;

5. 本站为非盈利性的个人网站,所有内容不会用来进行牟利,也不会利用任何形式的广告来间接获益,纯粹是为了广大技术爱好者提供技术内容和技术思想的分享性交流网站。

`timescale 1ns/1ps //时间刻度为1 ns

module top_sim

(

);

reg CLK;

initial

begin

CLK = 1'b0;

#4;

forever

#4 CLK = ~CLK; //duty cycle 50%, period 8 ns; frequency 125Mhz

end

endmodule

Modelsim 仿真波形

`timescale 1ns/1ps //时间刻度为1 ns

module top_sim

(

);

reg CLK;

initial

begin

CLK = 1'b0;

#4;

forever

#4 CLK = ~CLK; //duty cycle 50%, period 8 ns; frequency 125Mhz

end

endmodule

Modelsim 仿真波形

在设置时间尺度是也可直接指定时间单位或由关键字parameter定义的参数指定,修改缺省的 由`timeschale定义的时间尺度。

例:

parameter PERIOD = 10 ; reg CLK; initial begin CLK = 1'b0; #(PERIOD/2); forever #(PERIOD/2) CLK = ~CLK; end

2. 延迟:

赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端变量赋值之间的时间延时。

在设置时间尺度是也可直接指定时间单位或由关键字parameter定义的参数指定,修改缺省的 由`timeschale定义的时间尺度。

例:

parameter PERIOD = 10 ; reg CLK; initial begin CLK = 1'b0; #(PERIOD/2); forever #(PERIOD/2) CLK = ~CLK; end

2. 延迟:

赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端变量赋值之间的时间延时。

从波形可以看出,虽然开始ta,tb 有多次变化,由于变化的时间间隔都不足10个单位,因此tc并没有得到ta+tb的结果,只有在ta==4’b0110, tb==4’b0001的时刻开始,ta,tb稳定持续10个时间单位后,tc才得到ta+tb的值。所以连续赋值语句能否更新,是从参与计算的变量最近的时刻是否满足延迟时间的需求而定。

从波形可以看出,虽然开始ta,tb 有多次变化,由于变化的时间间隔都不足10个单位,因此tc并没有得到ta+tb的结果,只有在ta==4’b0110, tb==4’b0001的时刻开始,ta,tb稳定持续10个时间单位后,tc才得到ta+tb的值。所以连续赋值语句能否更新,是从参与计算的变量最近的时刻是否满足延迟时间的需求而定。

从仿真波形可以清楚看出,内部延迟与外部延迟的区别。

在建模时应注意各种delay的选择与使用。

从仿真波形可以清楚看出,内部延迟与外部延迟的区别。

在建模时应注意各种delay的选择与使用。